## 実規模半導体生産ラインに対するスケジューリング

01307154 大阪大学 田地宏一 TAJI Kouichi

大阪大学 \*宮崎泰輔 MIYAZAKI Taisuke

01303394 大阪大学 田村坦之 TAMURA Hiroyuki

(株) 日立製作所 増井知幸 MASUI Tomoyuki (株) 日立製作所 岩田義雄 IWATA Yoshio

### 1 はじめに

半導体生産においても、企業間の競争の激化などにより、効率のよいスケジューリングが求められるようになった。これまでは機械の稼働率の向上を目的としたディスパッチングルールによってスケジューリングが行われてきた[1,2]. しかし、納期の遵守といった新しい需要にこたえるためライン全体を考慮に入れたスケジューリングが必要である.

本論文では、まず半導体生産ラインのモデルを作成 し、局所探索法を用いたスケジューリング法を提案す る. また、初期解の作成法についても考案する. さら に計算実験により、提案した手法の有効性について考 察する.

### 2 半導体生産ラインモデル化

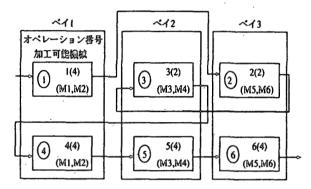

半導体は、全く処理の施されていないウェハに、何層かにわたって処理を施すことによって生産される.機械は同じ工程を繰り返し行うだけでなく、その機械で前の層の工程の処理を行ったウェハに対して、再び同じあるいは別の処理を行わなければならないという特徴を持つ.ウエハはロットと呼ばれる数十枚を単位としてラインの中を移動して行く.このように、1つのロットが同じベイに何度も戻ってくるという特徴を取り入れて作成したモデルの例を図1に示す.図1では、ベイの数が3つ、工程数は6、機械台数は6台である.

このモデル上でスケジューリングを行う問題はジョブショップ問題をさらに複雑にした形になっている.スケジュールを決めるためには、ロットの各工程を処理する機械の割り当てと、機械が作業するときの順序を決めなければならないが、図1のような小さい規模のモデルでさえも、各工程を機械に割り当てる組合せの数は2<sup>21</sup>通り存在し、厳密解を求めることは非常に困難であると考えられる.そこで次節では、局所探索法

図 1: 半導体生産ラインのモデル

を用いたスケジューリング法について述べる.

# 3 局所探索法によるスケジューリング

前節で提案したモデル上で滞留時間を最小化するスケジュールを考える.上で述べたように厳密解を求めるのは難しいので、ここでは swap 近傍を用いて局所探索法を行うことにする.近傍としては、各工程を処理する機械の割り当てのみを交換するというものも考えられる.しかし、与えられた割り当てに対する最適なスケジュールを求めるには、ジョブショップと同様の問題を解かねばならない[3].そのため、以下のような swap 近傍を用いる.

[swap 近傍] 2 つの工程の、処理する機械の割り当てとその機械上での処理する順序の組を入れ換えることによってできる実行可能なスケジュールの集合.

解の改善方法としては FIRST 改善を用いた.

局所探索法の結果の善し悪しは、初期解に依存ところが大きいといわれている. このため、本研究では次

の2つの方法(方法1,方法2)で初期解を作成する.

**方法1** ロットがラインに入った順に、ロットの工程を 1工程ずつ順番にいずれかの機械に割り当てる.

方法2 ロットがラインに入った順に, ロットの全ての 工程を作業することのできる機械に割り当てる.

また、今回採用した近傍では、局所探索中に各機械で の作業工程数は変化しないため、初期解での各機械に おける作業工程の数が均等になるように割り当てた.

### 4 数值実験

前節で述べた方法を用いて、さまざまな大きさの問題に対して計算実験を行った。実験は、PentiumII 450MHz、メモリ 64MB、OSは Windows NT の計算機を使用し、Visual C++で行った。結果を表 1、2に示す、表の中で、サイズはモデルの大きさを意味し、(ベイの数)×(ベイ内の機械台数)で表している。また、計算時間は局所最適解を見つけるまでに要する時間、滞留時間は局所解での滞留時間を表している。数値はそれぞれ 10 個の初期解から計算したものの平均値である。まず、予備実験として 2 つの初期解生成法(方法 1、2)についての比較を行った。その結果、計算時間と局所解での滞留時間は、ともに方法 1 のほうが優れていることが分かった。したがって、これ以後の数値実験において、初期解の作成には方法 1 を用いた。

表 1: 横方向に拡大した場合の結果

| 20 1. D(23) N = 10.70 D = 2.70 D |      |          |       |  |

|----------------------------------|------|----------|-------|--|

| サイズ                              | 工程数  | 計算時間 (秒) | 滞留時間  |  |

| 3 × 2                            | 6    | 1 秒未満    | 143.0 |  |

| 4 × 2                            | 8    | 1.5      | 184.2 |  |

| $5 \times 2$                     | . 10 | 8.5      | 314.4 |  |

| 6 × 2                            | 12   | 46.6     | 450.4 |  |

表 2: 縦方向に拡大した場合の計算結果

| サイズ          | 工程数 | 計算時間 (秒) | 滞留時間  |

|--------------|-----|----------|-------|

| $3 \times 2$ | 6   | 1 秒未満    | 143.0 |

| $3 \times 3$ | 9   | 4.6      | 205.8 |

| $3 \times 4$ | 12  | 126.9    | 392.6 |

| $3 \times 5$ | 15  | 785.2    | 607.1 |

表 1, 2 から, 計算時間は急激に増大していることがわかる. また、工程数が同じでもベイ内の機械台数を増やしたときのほうが, ベイ数を増やしたときより計算時間がかかることが分かる. これは, ベイ内の機械台数が増加すると機械の割り当ての組み合わせの数が大きくなるためである

### 5 結論と今後の課題

数値実験の結果、 $3 \times 5$  の問題に対して約 13 分の計算時間を要した.一方、実際の半導体生産ラインは工程数が約  $20 \times 10$  あるため、実際のラインに本論文のこの手法を適用した場合、このままでは、再スケジューリングを前提としたスケジュール作成時間の約 10 分では、スケジュールを作成することができないと考えられる.今後の課題として以下のようなことがあげられる.

- 計算時間を短縮するため、局所探索法を行うとき の探索領域に制限を加えるなどの改良を行う.

- ◆ さらに良い初期解を作成する発見的手法を考案する.

- より実際のラインに近づけるために、メンテナンス時間や初期状態での機械の作業時間を考慮する。

また、ロットの数を増加する。

#### 参考文献

- L. M. Wein, "Scheduling Semiconductor Wafer Fabrication," *IEEE Transactions of Semiconductor Manufacturing*, Vol. 1, No. 3, pp. 115-130, 1988.

- [2] S. H. Lu, D. Ramaswamy and P. R. Kumar, "Efficient Schedulig Policies to Reduce Mean and Variance on Cycle-Time in Semiconductor Manufacturing Plants," *IEEE Transactions on Semiconductor Manufacturing*, Vol. 7, No. 3, pp. 374-388, 1994.

- [3] 田地 宏一, 宮崎泰輔, 田村坦之, 増井知幸, 岩田義雄, "半導体生産スケジューリングのモデル化とその厳密解,"第43回システム制御情報学会講演会講演論文集, pp. 517-518, 1999年5月.